# HT2144

## STEREO 2.1W Non-Clip DIGITAL AUDIO POWER AMPLIFIER

## Overview

HT2144 is a digital audio power amplifier IC with maximum output of 2.1W (RL=4 $\Omega$ )×2ch. HT2144 has a "Pure Pulse Direct Speaker Drive Circuit" which directly drives speakers while reducing distortion of pulse output signal and reducing noise on the signal, and realizes the highest standard low distortion rate characteristics and low noise characteristics among digital amplifier ICs for mobile use.

In addition, circuit design with fewer external parts can be made depend on the condition of use because corresponds to filter less.

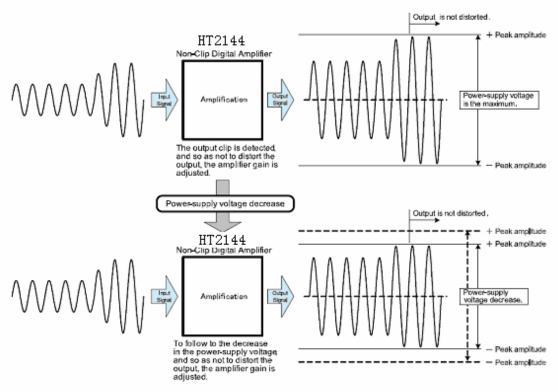

The HT2144 features Heroic original non-clip output control function which detects output signal clip due to the over level input signal and suppress the output signal clip automatically. Also the non-clip output control function can adapt the output clip caused by power supply voltage down with battery. This is the difference from the traditional AGC (Auto Gain Control) or ALC (Auto Level Control) circuit. Attack time and release time can be freely set by external resistances or capacitances.

The independent power-down function for L channel and R channel minimizes consumption current at standby. As for protection function, overcurrent protection function for speaker output terminal, overtemperatue protection function for inside of the device, and low supply voltage malfunction preventing function are prepared.

## Features

Maximum output

- 2.1 W×2ch (VDDP=VDDA=5.0V, RL=4 $\Omega$ , THD+N=1%)

- 0.75 W×2ch (VDDP=VDDA=3.6V, RL=8 $\Omega$ , THD+N=1%)

- Distortion Rate (THD+N)

0.03 % (VDDP=VDDA=3.6V, RL=8Ω, Po=0.4W, 1kHz)

Residual Noise

40µVrms (VDDP=VDDA=3.6V, Av=12dB)

Efficiency

84 % (VDDP=VDDA=3.6V, RL=8Ω, Po=600mW)

- 78 % (VDDP=VDDA=3.6V, RL=8 $\Omega$ , Po=100mW)

- S/N Ratio

95dB (VDDP=VDDA=3.6V, Av=12dB)

Channel separation

95dB (VDDP=VDDA=3.6V, RL=8Ω, Av=18dB, 1kHz)

- $\cdot$  Over-current Protection function

- Thermal Protection function

- Low voltage Malfunction Prevention function

- 2ch independent power-down control function

- Power-down High speed Recovery function

- Package

Lead-free 16-pin WLCSP Lead-free 20-pin QFN Lead-free 20-pin TSSOP

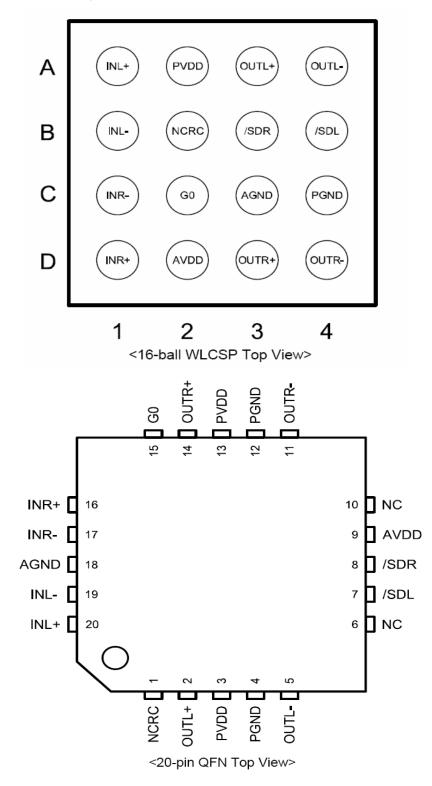

## Terminal configuration

-3- 共18页

## Terminal function

#### • WLCSP16

| N⁰ | Name  | I/O   | Function                                      |  |  |  |

|----|-------|-------|-----------------------------------------------|--|--|--|

| A1 | INL+  | А     | ositive input terminal (differential +) Lch   |  |  |  |

| A2 | PVDD  | Power | Power supply for output                       |  |  |  |

| A3 | OUTL+ | 0     | Positive output terminal (differential +) Lch |  |  |  |

| A4 | OUTL- | 0     | Negative output terminal (differential -) Lch |  |  |  |

| B1 | INL-  | А     | Negative input terminal (differential -) Lch  |  |  |  |

| B2 | NCRC  | I/O   | Non-Clip control terminal                     |  |  |  |

| B3 | /SDR  | I     | Shut-down terminal for Rch                    |  |  |  |

| B4 | /SDL  | I     | Shut-down terminal for Lch                    |  |  |  |

| C1 | INR-  | А     | Negative input terminal (differential -) Rch  |  |  |  |

| C2 | G0    | I     | Gain setting terminal                         |  |  |  |

| C3 | AGND  | GND   | GND for analog circuits                       |  |  |  |

| C4 | PGND  | GND   | GND for output                                |  |  |  |

| D1 | INR+  | А     | Positive input terminal (differential +) Rch  |  |  |  |

| D2 | AVDD  | Power | Power supply for analog circuits              |  |  |  |

| D3 | OUTR+ | 0     | Positive output terminal (differential +) Rch |  |  |  |

| D4 | OUTR- | 0     | Negative output terminal (differential -) Rch |  |  |  |

(Note) I: Input terminal O: Output terminal A: Analog terminal

-4- 共18页

#### · QFN20

| N⁰ | Name  | I/O   | Function                                      |  |  |  |

|----|-------|-------|-----------------------------------------------|--|--|--|

| 1  | NCRC  | I/O   | Non-Clip control terminal                     |  |  |  |

| 2  | OUTL+ | 0     | ositive output terminal (differential +) Lch  |  |  |  |

| 3  | PVDD  | Power | Power supply for output                       |  |  |  |

| 4  | PGND  | GND   | GND for output                                |  |  |  |

| 5  | OUTL- | 0     | Negative output terminal (differential -) Lch |  |  |  |

| 6  | NC    | -     | Non connection or connect to AGND             |  |  |  |

| 7  | /SDL  | I     | Shut-down terminal for Lch                    |  |  |  |

| 8  | /SDR  | I     | Shut-down terminal for Rch                    |  |  |  |

| 9  | AVDD  | Power | Power supply for analog circuits              |  |  |  |

| 10 | NC    | -     | Non connection or connect to AGND             |  |  |  |

| 11 | OUTR- | 0     | Negative output terminal (differential -) Rch |  |  |  |

| 12 | PGND  | GND   | GND for output                                |  |  |  |

| 13 | PVDD  | Power | Power supply for output                       |  |  |  |

| 14 | OUTR+ | 0     | Positive output terminal (differential +) Rch |  |  |  |

| 15 | G0    | I     | Gain setting terminal                         |  |  |  |

| 16 | INR+  | А     | Positive input terminal (differential +) Rch  |  |  |  |

| 17 | INR-  | А     | Negative input terminal (differential -) Rch  |  |  |  |

| 18 | AGND  | GND   | GND for analog circuits                       |  |  |  |

| 19 | INL-  | А     | Negative input terminal (differential -) Lch  |  |  |  |

| 20 | INL+  | А     | Positive input terminal (differential +) Lch  |  |  |  |

(Note) I: Input terminal O: Output terminal A: Analog terminal

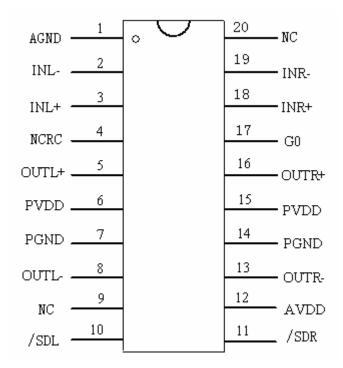

#### • TSSOP20

| N⁰ | Name  | I/O   | Function                                      |  |  |

|----|-------|-------|-----------------------------------------------|--|--|

| 1  | AGND  | GND   | GND for analog circuits                       |  |  |

| 2  | INL-  | А     | Negative input terminal (differential -) Lch  |  |  |

| 3  | INL+  | А     | Positive input terminal (differential +) Lch  |  |  |

| 4  | NCRC  | I/O   | Non-Clip control terminal                     |  |  |

| 5  | OUTL+ | 0     | Positive output terminal (differential +) Lch |  |  |

| 6  | PVDD  | Power | Power supply for output                       |  |  |

| 7  | PGND  | GND   | GND for output                                |  |  |

| 8  | OUTL- | 0     | Negative output terminal (differential -) Lch |  |  |

| 9  | NC    | -     | Non connection or connect to AGND             |  |  |

| 10 | /SDL  |       | Shut-down terminal for Lch                    |  |  |

| 11 | /SDR  |       | Shut-down terminal for Rch                    |  |  |

| 12 | AVDD  | Power | Power supply for analog circuits              |  |  |

| 13 | NC    | -     | Non connection or connect to AGND             |  |  |

| 14 | OUTR- | 0     | Negative output terminal (differential -) Rch |  |  |

| 15 | PGND  | GND   | GND for output                                |  |  |

| 16 | PVDD  | Power | Power supply for output                       |  |  |

| 17 | OUTR+ | 0     | Positive output terminal (differential +) Rch |  |  |

-5- 共18页

## HT2144

| 18        | G0                                                             | I | Gain setting terminal                        |  |  |  |

|-----------|----------------------------------------------------------------|---|----------------------------------------------|--|--|--|

| 19        | INR+                                                           | Α | Positive input terminal (differential +) Rch |  |  |  |

| 20        | INR-                                                           | А | Negative input terminal (differential -) Rch |  |  |  |

| (Note) I: | (Note) I: Input terminal O: Output terminal A: Analog terminal |   |                                              |  |  |  |

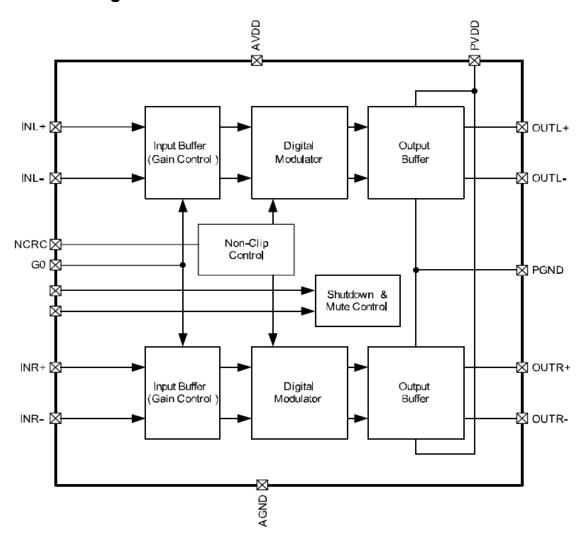

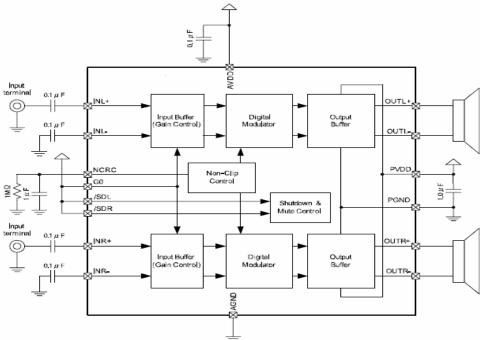

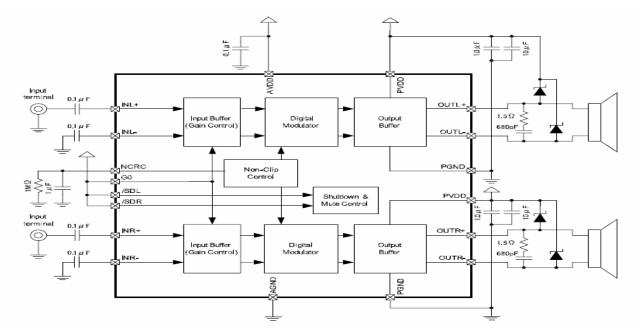

## Block diagram

-6- 共18页

## Description of operating functions

#### • Digital Amplifier Function

HT2144 has digital amplifiers with analog and digital input, PWM pulse output, Maximum output of  $2.1W(RL=4\Omega)\times 2ch$ .

Distortion of PWM pulse output signal and noise of the signal is reduced by adopting "Pure Pulse Direct Speaker Drive Circuit"

In addition, HT2144 has been designed so that high-efficiency can be maintained within an average power range (100mw or so) that is used for mobile terminal.

#### First Stage Amplifier Gain Setting Function

G0 terminal can set the Gain of HT2144. When Non-Clip function is disabled, the relation between G0 terminal setting and Gain is as follows.

#### Digital Amplifier Gain Setting

| G0 | Gain | Input Impedance(Z <sub>IN</sub> ) |

|----|------|-----------------------------------|

| L  | 12dB | 44kΩ                              |

| Н  | 18dB | 28kΩ                              |

Note) H and L indicates logic High and logic Low, respectively.

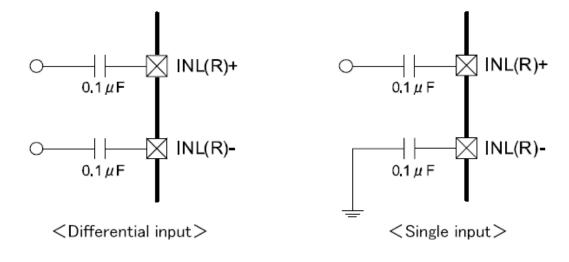

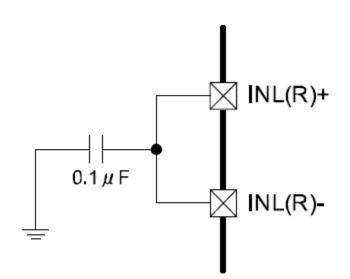

Input Lch differential input signals to INL+ terminal and INL- terminal through DC-cut capacitors (CIN). For single ended operation, input the signal to INL+ pin through the DC-cut capacitor (CIN). At this time, INL- pin must be connected to AVSS pin through a capacitor (CREF: same value as CIN). As with Lch, connect input signals to Rch.

## -7- 共18页

In addition, positive (+) and negative (-) sides of differential input pins (INL+ and INL-, or INR+ and INR-), input pins of the unused channel side, should be connected to each other and connected to AVSS through a capacitor.

Use a capacitor with the same capacitance  $(0.1\mu F)$  as that of a DC-cut capacitor in the channel side being used.

<Input terminal processing of unused channel side>

The lower cut-off frequency (fc) can be found from DC-cut capacitor (CIN) and input impedance (ZIN) as shown below.

fc=1/(2\*π\*ZIN\*CIN)

In order to reduce pop-noise, impedance in the differential input signal source is arranged. And, DC-cut capacitor (CIN) should be  $0.1\mu$ F or less.

## Non-Clip control Function

This is the function to control the output in order to obtain a maximum output level without distortion when an excessive input which causes clipping at the differential signal output is applied. That is, with the Non-Clip function, HT2144 lowers the Gain of the digital amplifier to an appropriate value so as not to cause the clipping at the differential signal output. And, HT2144 follows also to the clip of the output wave form due to the decrease in the power-supply voltage.

### HT2144

<Operation outline of Non-Clip control function>

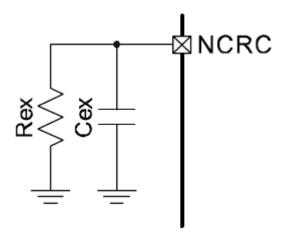

Connecting a resistor (Rex) and a capacitor (Cex) to NCRC terminal can set Attack Time and Release Time of the Non-Clip control. A temperature compensation type ceramic capacitor is recommended as capacitor (Cex).

The Attack time is a time interval until gain falls to target attenuation gain -3dB with a big signal input enough.

And, the Release Time is a time from target attenuation gain to not working of Non-Clip.

With the target attenuation gain of 10dB, the Attack Time and Release Time is as can above Table.

| Rex(M Ω )       | 1   | 4.7 | 1    | 1   |

|-----------------|-----|-----|------|-----|

| Cex(µF)         | 1   | 1   | 0.47 | 4.7 |

| Attack Time(ms) | 10  | 10  | 4.7  | 4.7 |

| Release Time(s) | 0.8 | 3.8 | 0.38 | 3.8 |

Resistor(Rex), Capacitor(Cex) and Attack Time, Release Time

Non-Clip control function can be invalidated by the NCRC terminal assumption H level fixation (AVDD potential) or L level fixation (GND). In that case, the following differences exist by the state of the NCRC terminal.

Difference of operation by state of NCRC terminal when Non-Clip control function is OFF.

| NCRC terminal            | Current increase<br>[mA] | Start up wait time<br>[sec] | Non-Clip function<br>ON/OFF change<br>in state of signal input. |

|--------------------------|--------------------------|-----------------------------|-----------------------------------------------------------------|

| L level (GND)            | 0.2 (Maximum)            | 0                           | Change is possible.                                             |

| H level (AVDD potential) | 0                        | 3*Rex*Cex                   | Change is prohibited.                                           |

Start up wait time: It means time until the signal input is permitted from Non-Clip function ON.

#### Protection Function

HT2144 has the following protection functions for the digital amplifier: Over-current Protection function, Thermal Protection function, and Low voltage Malfunction Prevention function.

#### **Over-current Protection function**

This is the function to establish the over-current protection mode when detecting a short circuit between HT2144 differential output pin and VSS, VDD, or another differential output. The function works independently for Lch and Rch. In the over current protection mode, the differential output pin becomes a high impedance state.

Setting /SDR pin to a logic Low state can cancel the Rch over current protection mode. Likewise, when setting /SDL pin to a logic Low level, the over current protection mode applied to Lch can be cancelled. In addition, turning on the power again can cancel the over current protection mode applied to Lch and Rch.

#### **Thermal Protection function**

This is the function to establish the thermal protection mode when detecting excessive high temperature of HT2144 itself. In the thermal protection mode, the differential output pin becomes Weak Low state (a state grounded through high resistivity). And, when HT2144 gets out of such condition, the protection mode is cancelled.

#### Low voltage Malfunction Prevention function

This is the function to establish the low voltage protection mode when AVDD pin voltage becomes lower than the detection voltage ( $V_{UVLL}$ ) for the low voltage malfunction prevention and to cancel the protection mode when AVDD pin voltage becomes higher than the threshold voltage ( $V_{UVLH}$ ) for its deactivation. In the low voltage protection mode, the differential output pin becomes Weak Low state (a state grounded through high resistivity). HT2144 will start up within the start-up time ( $T_{STUP}$ ) when the low voltage protection mode is cancelled.

#### • Power-down Function

This is the function to turn Rch into the power-down mode when setting /SDR terminal to a logic Low level and to turn Lch into the power-down mode when setting /SDL terminal to a logic Low level. The power-down mode stops all the functions and minimizes current consumption. At this time, the differential output signal becomes Weak Low state (a state grounded through high resistivity).

HT2144 will start up within the start-up time (Tstup) when setting /SDR and /SDL terminals to a logic High state.

#### Caution :

When using a device while Non-Clip function is ON, power down state of both channels is released and used.

Please do not adjust the AVDD power supply voltage to less than 2V, when set to power down with the voltage impressed to the PVDD power supply terminal.

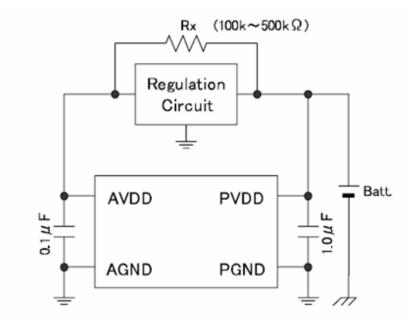

• Power up the PVDD supply voltage in conjunction with the AVDD regulation circuit when AVDD is generated by regulating PVDD.

• AVDD voltage should be within the range of  $2V \le AVDD \le PVDD$  as shown in the following figure when the AVDD

2008.7

regulation circuit needs to be stopped by power supply management.

<Example of measures for AVDD regulation circuit stop option>

Notes in example of the above-mentioned measures

• When a voltage is supplied to PVDD pin, decide a value of Rx so that the voltage at AVDD pin becomes a value within the range of  $2V \le AVDD \le PVDD$ .

A value of Rx is about  $100k\Omega$  to  $500k\Omega$ , because the power-down leakage current (AVDD current) of HT2144 is0.1µA typ. (2µA max.@125°C).

And, when an LSI other than HT2144 is connected to the same regulator, decide a value of Rx in consideration of all leakage currents.

• The regulator output may increase up to the supply voltage level (=PVDD voltage) such as a battery when load current is zero. Please carefully check if any problem such as LSI's withstand voltage would occur when an LSI other thanHT2144 is connected to the same regulator.

• This measure is effective only when a regulator whose output during a stop state becomes the high impedance state is used.

#### • Pop noise reduction function

The Pop Noise Reduction Function works in the cases of Power-on, Power-off, Power-down on, and Power-down off.

And, the pop-noise can be suppressed according to control the power down by the following procedure.

2008.7

- /SDR and /SDL terminal are assumed to be H, after power-on.

- · /SDR and /SDL terminal are assumed to be L, before Power-off.

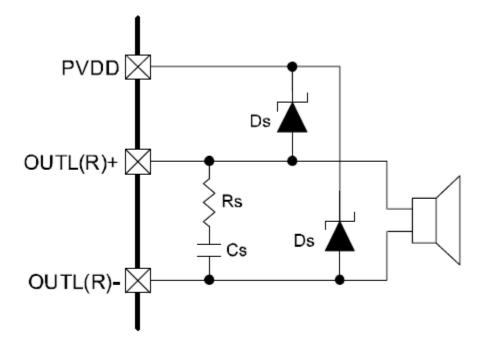

#### • Snubber Circuit and schottky barrier diode

It is necessary to connect the snubber circuit and schottky barrier diode with the output terminal to prevent IC destructionby the output short-circuit when using it on the following conditions. The constant and the circuit are as follows.

| Power supply voltage<br>range   | Load conditions                      | Snubber Circuit                                   | Schottky barrier diode    |

|---------------------------------|--------------------------------------|---------------------------------------------------|---------------------------|

| $2.7$ V $\leq$ PVDD $\leq$ 4.5V | RL=8 Ω<br>Wiring inductance ><br>4uH | Between OUT*+ and<br>OUT*-<br>Rs=1.5 Ω , Cs=330pF | Need less                 |

| 4.5V < PVDD ≦ 5.25V             | $R_L=4 \Omega$ or $8 \Omega$         | Between OUT*+ and<br>OUT*-<br>Rs=1.5 Ω , Cs=680pF | Between OUT** and<br>PVDD |

Recommended parts

Schottky barrier diode: ROHM, RB161VA-20

Forward current surge peak = 5A or more, Average forward current = 1A or more,

Forward voltage ( $I_F$ =1A) = 0.38V or less

<Snubber circuit and Schottky barrier diode>

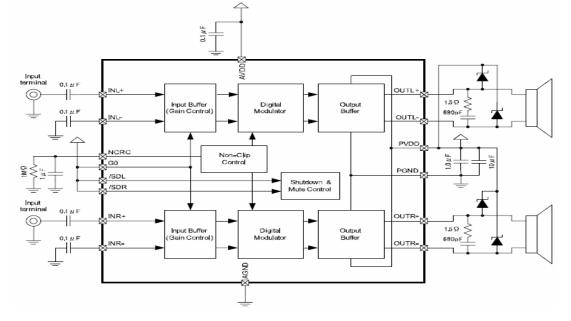

## Application circuit examples

#### • WLCSP16

• Snubber circuit and schottky barrier diode are unnecessary ( $2.7V \le PVDD \le 4.5V$ )

• Snubber circuit and schottky barrier diode are necessary (4.5V<PVDD)

When the IC is used at more than 4.5V power supply, use it with an additional capacitor of  $10\mu F$  or over between PVDD and GND.

Place a bypass capacitor as close as possible to each power supply pin of the IC.

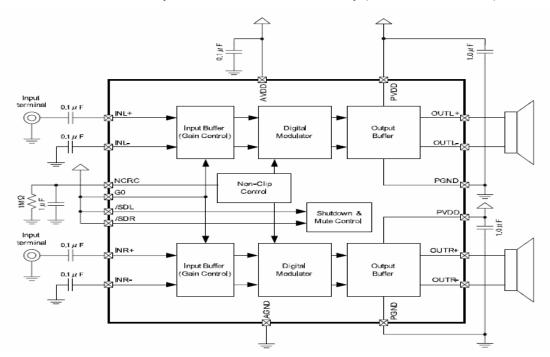

#### • QFN20/TSSOP20

• Snubber circuit and schottky barrier diode are unnecessary  $(2.7V \le PVDD \le 4.5V)$

• Snubber circuit and schottky barrier diode are necessary (4.5V<PVDD)

When the IC is used at more than 4.5V power supply, use it with an additional capacitor of  $10\mu F$  or over between PVDD and GND.

Place a bypass capacitor as close as possible to each power supply pin of the IC.

2008.7

-15- 共18页

## Cautions for Safety

Please observe the following restrictions to use HT2144 safely.

- The snubber circuit should be laid out within 3mm from the IC on the component side.

- The schottky barrier diode should be laid out within 3mm from the IC.

- Place a bypass capacitor, which is connected between PVDD and GND, together with a schottky barrier diode.

And, when no schottky barrier diode is required, place it within 3mm from the IC.

• When a LC filter is used, consider the following.

With a system of which an input signal in excess of a resonance frequency of a LC filter could be input, be sure to place a snubber circuit (insert  $13\Omega$ +330ns at the LC filter output) after the LC filter to prevent an over-current condition. The purpose is to prevent an over-current from flowing because an impedance of the speaker increases at the resonance frequency.

With a system of which a voltage at an input pin might exceed a supply voltage of VDDA/GND, use an external diode etc.to assure that the voltage does not exceed the absolute maximum rating.

## **Electrical Characteristic**

#### Absolute Maximum Ratings

| Item                                             | Symbol            | Min.    | Max.                  | Unit |

|--------------------------------------------------|-------------------|---------|-----------------------|------|

| Power supply terminal (PVDD) Voltage Range       | V <sub>DDP</sub>  | -0.3    | 6.0                   | V    |

| Power supply terminal (AVDD) Voltage Range       | V <sub>DDP</sub>  | -0.3    | 6.0                   | V    |

| Input terminal Voltage Range                     | V <sub>IN</sub>   | Vss-0.6 | V <sub>DDA</sub> +0.6 | V    |

| (Analog input terminals: INL+,INL-,INR+,INR-)    |                   |         |                       |      |

| Input terminal Voltage Range                     | V <sub>IN</sub>   | Vss-0.3 | V <sub>DDA</sub> +0.3 | V    |

| (Input terminals except the above-mentioned)     |                   |         |                       |      |

| Allowable dissipation (20QFN,Ta=25°C)            | P <sub>D25</sub>  |         | 1.56                  | W    |

| Allowable dissipation (20QFN,Ta=85 $^{\circ}$ C) | P <sub>D85</sub>  |         | 0.62                  | W    |

| Allowable dissipation (20QFN,Ta=25°C)            | P <sub>D25</sub>  |         | 3.63                  | W    |

| Allowable dissipation (20QFN,Ta=85 $^{\circ}$ C) | P <sub>D85</sub>  |         | 1.45                  | W    |

| Junction Temperature                             | T <sub>JMAX</sub> |         | 150                   | °C   |

| Storage Temperature                              | T <sub>STG</sub>  | -50     | 125                   | °C   |

|                                                  | I                 | 1       | 1                     | 1    |

Note) Absolute Maximum Ratings is values which must not be exceeded to guarantee device reliability and life, and when using a device in excess even a moment, it may immediately cause damage to device or may significantly deteriorate its reliability

With a system of which a voltage at an input pin might exceed a supply voltage of VDDA/GND, use an external diode to assure that the voltage does not exceed the absolute maximum rating.

\*1:  $\theta$ ja=50.0°C/W, conditions: HT2144 evaluation board (4 layers), dead calm

\*2: θja=64.0°C/W, conditions: HT2144 evaluation board (2 layers, without through-hole), dead calm

\*3: θja=27.5°C/W, conditions: 4 layers, through-hole, copper foil 65μm, dead calm

#### Recommended Operating Condition

| Item                                             | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|--------|------|------|------|------|

| Power Supply Voltage(PVDD)                       | VDDP   | 2.7  | 3.6  | 5.25 | V    |

| Power Supply Voltage(AVDD)                       | Vdda   | 2.7  | 3.6  | 5.25 | V    |

| Operating Ambient Temperature                    | Ta     | -40  | 25   | 85   | °C   |

| Speaker Impedance (4.5V < PVDD)                  | RL     | 4    |      |      | Ω    |

| Speaker Impedance (2.7V $\leq$ PVDD $\leq$ 4.5V) | R∟     | 8    |      |      | Ω    |

Note) Do not use under a condition other than the recommended operating conditions.

$PVDD \ge AVDD$  (contain power supply start up) must be met.

The rising time of PVDD and AVDD should be more than  $1\mu~{\rm s}$  .

| ●DC Characteristics (VSS=0V, VDDP= VDDA =2.7V to 5.25V, Ta=-40°C to 85°C, unless |  |

|----------------------------------------------------------------------------------|--|

| otherwise specified)                                                             |  |

| Item                                                  | Symbol            | Conditions                                            | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|-------------------|-------------------------------------------------------|------|------|------|------|

| AVDD power supply<br>start-up threshold voltage       | V <sub>UVLH</sub> |                                                       |      | 2.2  |      | V    |

| AVDD power supply<br>shut-down threshold voltage      | V <sub>UVLL</sub> |                                                       |      | 2.0  |      | V    |

| /SDL, /SDR, G0 terminal H level input voltage         | V <sub>IH</sub>   |                                                       | 1.35 |      |      | V    |

| /SDL, /SDR, G0 terminal L level input voltage         | V <sub>IL</sub>   |                                                       |      |      | 0.35 | V    |

| AVDD consumption current                              | I <sub>DD</sub>   | V <sub>DDA</sub> =3.6v,no load                        |      | 6.0  |      | mA   |

| PVDD consumption current                              | I <sub>DD</sub>   | V <sub>DDA</sub> =3.6v,no<br>load,<br>no signal input |      | 2.0  |      | mA   |

| Consumption current in<br>power-down mode AVDD + PVDD | I <sub>PD</sub>   | /SDL=/SDR=V <sub>SS</sub><br>T <sub>a</sub> =25℃      |      | 0.1  |      | uA   |

## •AC characteristics (Vss=0V, Vddp= Vdda =2.7V to 5.25V, Ta=-40 $^\circ C$ to 85 $^\circ C$ , unless otherwise specified)

| Item                       | Symbol | Conditions                                     | Min | Тур | Max | Unit |

|----------------------------|--------|------------------------------------------------|-----|-----|-----|------|

| Start-up time              | TSTUP  |                                                |     | 3.5 |     | ms   |

| Input cut-off<br>frequency | fc     | C <sub>IN</sub> =0.1uF,Av=18dB                 |     | 57  |     | Hz   |

| Attack time                | Τατ    | $V_{DDA}$ =3.6v,g=10dB,Cex=1uF,Rex=1M $\Omega$ |     | 10  |     | ms   |

| Release time               | Trl    | $V_{DDA}$ =3.6v,g=10dB,Cex=1uF,Rex=1M $\Omega$ |     | 0.8 |     | S    |

| Carrier clock<br>frequency | fрwм   |                                                |     | 1.0 |     | MHz  |

#### Analog Characteristics

(VSS=0V, VDDP= VDDA =3.6V, RL=8Ω, Ta=25°C, Non-Clip function=OFF, no snubber circuit, no schottky barrier diode,unless otherwise specified)

| Item                                         | Symbol           | Conditions                                  | Min | Тур  | Max | Unit              |

|----------------------------------------------|------------------|---------------------------------------------|-----|------|-----|-------------------|

| Maximum output                               | Po               | R <sub>L</sub> =4Ω,<br>f=1kHz,THD+N=10%,    |     | 2.1  |     | W                 |

|                                              |                  | $V_{\text{DDP}} = V_{\text{DDA}} = 5V$      |     |      |     |                   |

|                                              |                  | R <sub>L</sub> =8Ω,<br>f=1kHz,THD+N=10%     |     | 0.75 |     | W                 |

| Voltage Gain                                 | Av               | G0=L                                        |     | 12   |     | dB                |

|                                              |                  | G0=H                                        |     | 18   |     | dB                |

| Total Harmonic Distortion Rate<br>(BW:20kHz) | THD+N            | R <sub>L</sub> =8Ω, Po=0.4W,<br>f=1kHz      |     | 0.03 |     | %                 |

| Residual Noise (A-Filter)                    | N                | Av=12dB                                     |     | 40   |     | uV <sub>rms</sub> |

| Signal /Noise Ratio<br>(BW:20kHz A-Filter)   | SNR              | Av=12dB                                     |     | 95   |     | dB                |

| Channel Separation Ratio                     | CS               | 1kHz                                        |     | 95   |     | dB                |

| Power supply rejection ratio                 | PSRR             | 217Hz (to P <sub>VDD</sub> )                |     | -85  |     | dB                |

| Maximum Efficiency                           | η                | R <sub>L</sub> =8Ω, Po=600mW                | 1   | 84   | 1   | %                 |

|                                              |                  | R <sub>L</sub> =8Ω, Po=100mW                |     | 78   |     | %                 |

| Output offset voltage                        | Vo               |                                             |     | ±20  |     | mV                |

| Frequency characteristics                    | f <sub>RES</sub> | C <sub>IN</sub> =0.1µF, f=100Hz to<br>20kHz | -3  | -    | 1   | dB                |

| Non-Clip<br>maximum attenuation gain         | Aa               |                                             |     | -10  |     | dB                |

Note) All the values of analog characteristics were obtained by using our evaluation circumstance.

Depending upon parts and pattern layout to use, characteristics may be changed.

$8\Omega$  or  $4\Omega$  resistor and  $30\mu$ H coil are used as an output load in order to obtain various digital amplifier characteristics.

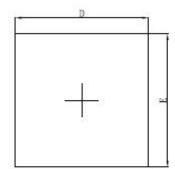

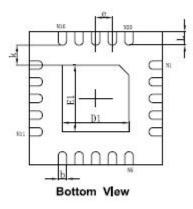

## Physical Dimensions

QFNWB4×4-20L (PO. 50TO. 75/0. 85) PACKAGE OUTLINE DIMENSIONS

Side View

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |             |  |

|--------|--------------|---------------|----------------------|-------------|--|

|        | Min.         | Max.          | Min.                 | Max.        |  |

| Α      | 0.700/0.800  | 0.800/0.900   | 0.028/0.031          | 0.031/0.035 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002       |  |

| A3     | 0.203REF.    |               | 0.008                | REF.        |  |

| D      | 3.900        | 4.100         | 0.154                | 0.161       |  |

| E      | 3.900        | 4.100         | 0.154                | 0.161       |  |

| D1     | 1.900        | 2.100         | 0.075                | 0.083       |  |

| E1     | 1.900        | 2.100         | 0.075                | 0.083       |  |

| k      | 0.200MIN.    |               | 0.008MIN.            |             |  |

| b      | 0.180        | 0.300         | 0.007                | 0.012       |  |

| е      | 0.500TYP.    |               | 0.020TYP.            |             |  |

| L      | 0.300        | 0.500         | 0.012                | 0.020       |  |

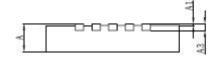

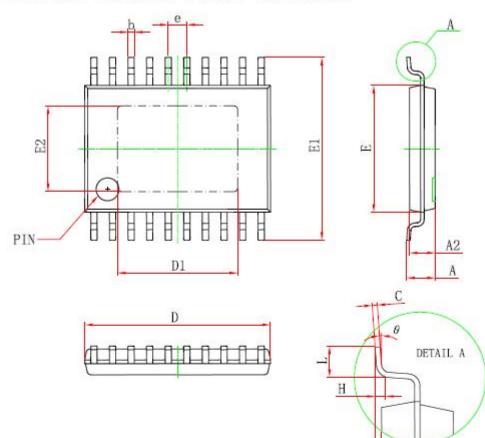

## TSSOP20/PP PACKAGE OUTLINE DIMENSIONS

| Symbol | Dimensions In | n Millimeters | Dimensions In Inches |       |  |

|--------|---------------|---------------|----------------------|-------|--|

|        | Min           | Max           | Min                  | Max   |  |

| D      | 6.400         | 6.600         | 0.252                | 0.259 |  |

| Dl     | 4.100         | 4.300         | 0.165                | 0.169 |  |

| E      | 4.300         | 4.500         | 0.169                | 0.177 |  |

| ь      | 0.190         | 0.300         | 0.007                | 0.012 |  |

| c      | 0.090         | 0.200         | 0.004                | 0.008 |  |

| El     | 6.250         | 6.550         | 0.246                | 0.258 |  |

| E2     | 2.900         | 3.100         | 0.114                | 0.122 |  |

| A      | 5 ab          | 1.100         |                      | 0.043 |  |

| A2     | 0.800         | 1.000         | 0.031                | 0.039 |  |

| A1     | 0.020         | 0.150         | 0.001                | 0.006 |  |

| e      | 0.65 (BSC)    |               | 0.026(BSC)           |       |  |

| L      | 0.500         | 0.700         | 0.02                 | 0.028 |  |

| н      | 0.25(TYP)     |               | 0.01(                | TYP)  |  |

| 0      | 1 °           | 7 °           | 1 °                  | 7 *   |  |

A1